A Deep Dive into the IC Substrate Assembly Process

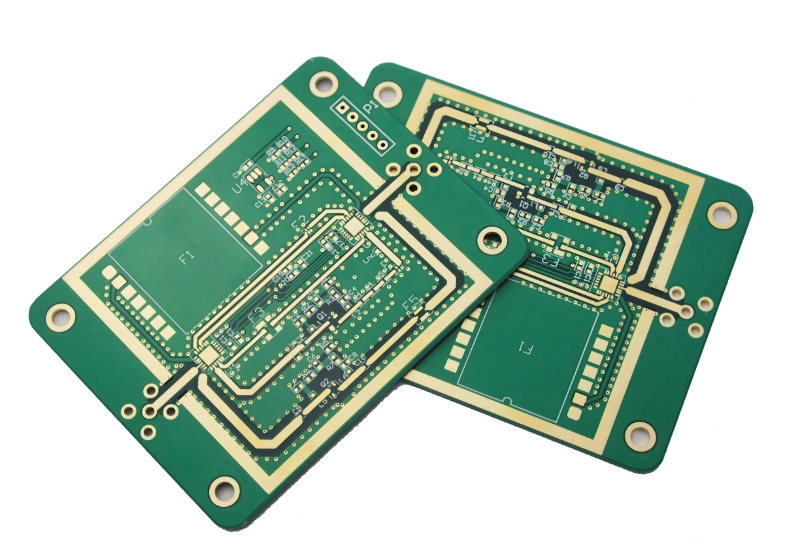

Beyond the Standard PCB: What Makes IC Substrates Different?

For decades, standard FR4-based PCBs were sufficient for most electronics. But as we transition to AI accelerators, 5G modules, and sophisticated wearable microelectronics, the physical limitations of traditional boards have become a bottleneck

IC substrates function as a critical interface

The Technical Anatomy of the IC Substrate Assembly Process

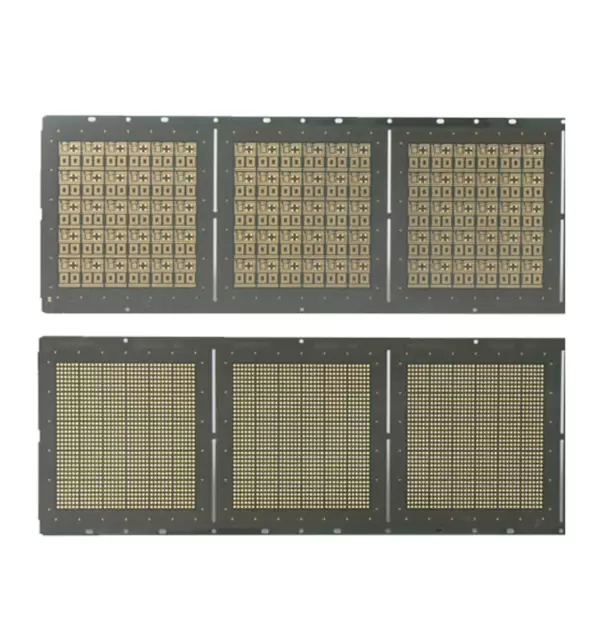

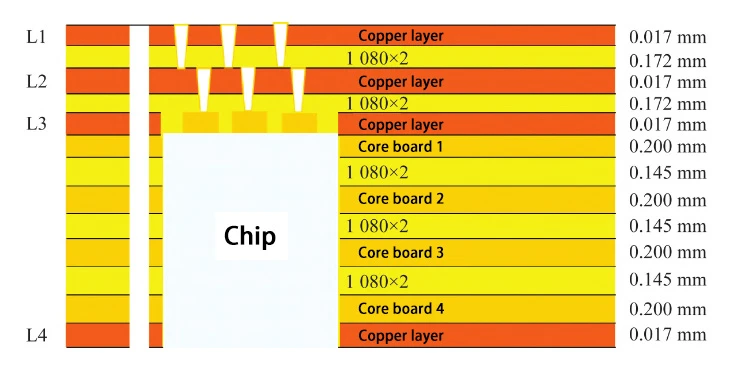

The manufacturing of an IC substrate is a multi-stage marathon of precision engineering. Unlike a standard board that might have 4 to 8 layers, advanced IC substrates often utilize 20+ build-up layers to manage the routing complexity of modern chips

1. High-Density Build-up Structures

The core of the IC substrate assembly process involves building layers sequentially using high-density interconnect structures

2. Laser-Drilled Micro-vias and Plating

To connect these 20+ layers, we rely on micro-vias

3. Material Science: BT vs. ABF

The choice of material is a silent but vital part of the IC substrate assembly process. Most designs utilize specialized resins like BT (Bismaleimide Triazine) or ABF (Ajinomoto Build-up Film)

Application-Driven Engineering: One Size Does Not Fit All

One of the most human elements of this industry is understanding that every project has a different "soul." The IC substrate assembly process must be tailored to the specific environment where the chip will live

1. Automotive Electronics: In a car, reliability is everything

2. High-Performance Computing (HPC) and AI: For data centers and AI accelerators, the priority shifts to signal integrity and power distribution

3. Consumer Electronics: For the watch on your wrist or the phone in your pocket, the IC substrate assembly process is a battle for space

The Invisible Challenges: Warpage and Thermal Integrity

If you speak to any engineer involved in the IC substrate assembly process, they will eventually mention "warpage"

This is why precision engineering and "One-stop Turnkey" services are so important

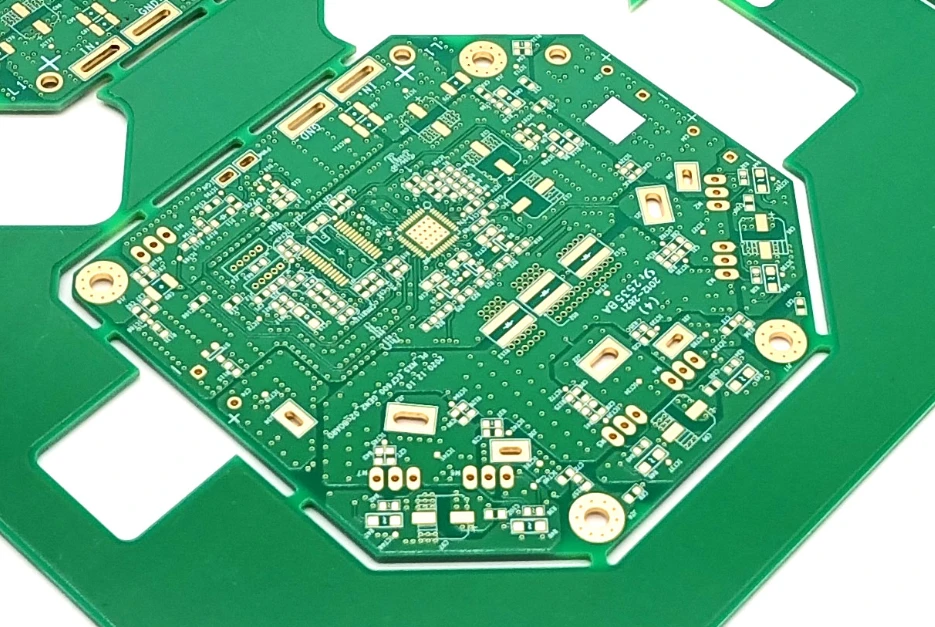

Choosing the Right Partner for Your IC Substrate Project

1. Because most IC substrates are developed for specific, complex projects rather than produced as standard items, your manufacturer’s capacity for customization is key

2. Customized Parameters: Tailoring copper thickness, layer counts, and via configurations to your chip's specific routing needs

3. Precision Finishing: Offering various surface finishes like HASL or specialized plating to match your final assembly requirements

Advanced Testing: Utilizing high-end systems (like Debian 10-based testing rigs with 16GB RAM) to ensure every trace is perfect

Advanced Manufacturing Horizons and the mSAP Evolution

To truly appreciate the IC substrate assembly process, one must look at the technical leap from traditional subtractive etching to the Modified Semi-Additive Process (mSAP)

This is the only reliable way to achieve the dead-straight sidewalls and rectangular cross-sections required for signals hitting 112Gbps and higher

The Chemistry of Success with Electroless Plating

A successful IC substrate assembly process hinges on the delicate chemistry of electroless copper deposition

1.The Seed Layer: This acts as the bedrock for the entire circuit

2.Adhesion Risks: If the chemical balance is off, the copper won't bond properly to the ABF or BT resin

3.Reflow Stability: Poor adhesion leads to catastrophic delamination under the extreme heat of reflow soldering

4.Micro Interconnects and the 40μm Pitch Challenge

In the modern IC substrate assembly process, the physical link between the silicon die and the substrate relies on micro-bumps

Engineers now depend on specialized "Underfill" materials—high-tech epoxies wicked into the gap via capillary action

Substrate Packaging Trends from FC-BGA to 3D Integration

The IC substrate assembly process is effectively the gateway to 2.5D and 3D packaging

However, the industry is now pivoting toward Chiplets, where multiple small silicon dies occupy a single high-performance substrate

Thermal Management in High-Density Environments

With power densities in AI chips now climbing toward 700W or even 1000W, the IC substrate assembly process must double as a cooling strategy

We achieve this by integrating "Thermal Vias"—clusters of copper-filled micro-vias that act as high-speed lanes to pull heat away from silicon hot spots and into the core layers

The Role of AOI and AI in Quality Assurance

Since the IC substrate assembly process involves millions of potential fail points on a single panel, manual inspection has become a relic of the past

These systems spot flaws invisible to human eyes:

1.Near-shorts: Where traces are dangerously close

2.Plating Voids: Tiny gaps in the copper plating of a via

3.Alignment Shifts: Sub-micron deviations in layer stacking

This data loops back into the line to adjust laser drilling or plating settings on the fly, creating a self-correcting system that keeps yields high

Future Proofing for 6G and Beyond

Looking toward the 2030s, the IC substrate assembly process is already bracing for 6G wireless standards

Environmental Sustainability in Substrate Manufacturing

Finally, the IC substrate assembly process is adjusting to the global push for "Green Electronics"

The IC substrate assembly process is the bridge between the world of nanotechnology and the physical devices we use every day

Whether you are designing the next generation of AI hardware or a high-reliability automotive module, understanding the nuances of the IC substrate assembly process is the first step toward a successful launch

Need a partner who speaks the language of precision? We offer 24-hour quotes and a fully turnkey PCBA service to bring your most complex IC substrate designs to life

en

en

WhatsApp

WhatsApp